JTAG チェーンの最初にないARMコアのデバッグ

テクニカル・ノート 17681

アーキテクチャ:

Arm

コンポーネント:

debugger

更新日:

2022/06/19 14:03

はじめに

本テクニカルノートでは、JTAGチェーン上の先頭以外のデバイスをデバッグする方法について説明します。

解説

C-SPY®では、デバッグするデバイスがJTAGチェーンの先頭にない場合、先行デバイスの情報を設定する必要があります。I-jet®プローブとEmuDiag.exeツールを使用して、この情報を収集してください。

JTAGチェーンの例

複数のJTAGデバイスを接続してチェーンを作成するには、デバイスのTDOを次のデバイスのTDIへと順に接続します。

次の図では、2個のデバイスがJTAGチェーンに接続されています。

どのデバイスが先頭?

ここでは、TDOがデバッグプローブに接続されているほうが 先頭 デバイスです。次の点に注意してください。

- 先頭 デバイスにはIDとしてTAP0(zero)が与えられます。

- 先頭 デバイスのデバッグでは、何も設定する必要はありません。

JTAGチェーンの先頭以外のデバイスのデバッグ方法

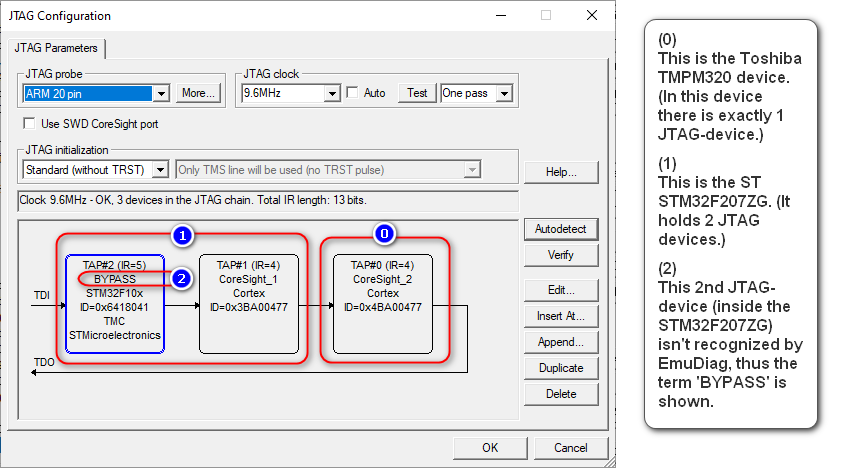

JTAGチェーンの先頭以外のデバイスをデバッグするには、以下のステップが必要です(以下の例のJTAGチェーンは、東芝のTMPM320-SKボードとST STM32F207ZGボードによって構築されています)。

- I-jetプローブを接続します。

- IAR Embedded Workbench for Arm®を起動してI-jet > EmuDiagを選択します。

- EmuDiag.exe上で、Test JTAGボタンをクリックします(JTAG Configurationのダイアログボックスが表示されます)。

- Autodetectボタンをクリックして、JTAGチェーンを表示します。

- 次の情報を記録しておいてください。

- ST STM32F207ZGのIDはTAP1。

- TAP0 デバイス(東芝TMPM320)はIR=4、すなわち、先行ビット数は4。

- EmuDiag.exeを閉じます。

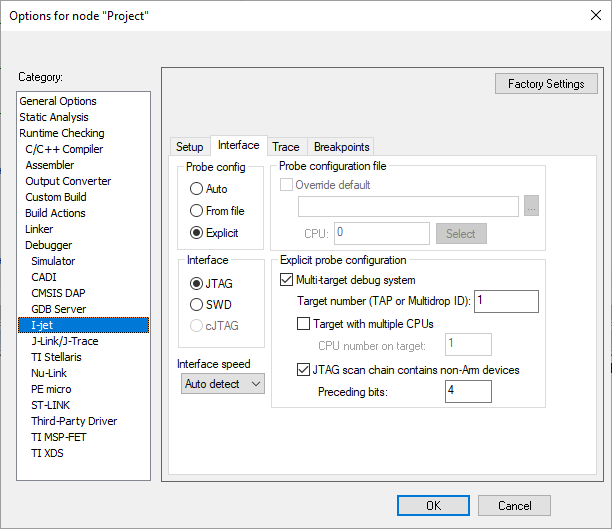

- Embedded Workbench for Arm上で、ST STM32F207ZGのプロジェクトを開き、Project(プロジェクト) > Options(オプション) > Debugger(デバッガ) > I-jet > Interface(インタフェース)を選択します。

- 以下を設定します:

- Probe config(プローブ設定)をExplicit(明示的)に設定。

- Multitarget debug system(複数ターゲットデバッグシステム)を選択。

- Target number(ターゲット)を1に設定。

- JTAG scan chain contains non-Arm devices(JTAGスキャンチェーンに非ARMデバイスを含む)を選択。

- Preceding bits(先行ビット)を4に設定。

- Setup(設定)タブをクリックして、Reset strategyを設定します。

- Cortexは、Core resetに設定。

- ARM 7/9 は、Software resetに設定。

- TRSTを使用するとすべてのコアがリセットされてしまうので、 TRST を使用しないreset strategyを選択することが重要です。

詳細情報

- I-jetおよび EmuDiag.exe については、C:\Program Files\IAR Systems\Embedded Workbench 9.0\arm\bin\emudiag.pdf にJTAGチェーンの詳細情報が記載されています。

- J-Linkについては、\arm\doc\JLink_J-TraceARM.pdfを参照してください。

Typical path は以下です。

C:\Program Files\IAR Systems\Embedded Workbench x.y\

ここで x.y common componentsのバージョンです。

まとめ

I-jetプローブはJTAGチェーン上のいずれのデバイスにも接続できます。I-jetを接続して、 EmuDiag.exeツールでJTAGチェーンに関する情報を収集し、その情報をC-SPYデバッガのOptions(オプション)ダイアログボックスに入力してください。

全ての製品名は、それぞれの所有者の商標または登録商標です。