在许多嵌入式项目中,RAM并非工程师们首要担忧的资源。早期原型通常能在评估板上顺畅运行,测试固件自然生长,内存占用感觉“足够用”。然后现实给了当头一棒。

新增一项功能。诊断系统扩展。安全更新引入新的缓冲区。突然间,RAM不再是冗余空间,而成了项目瓶颈。而一旦RAM成为制约因素,其后果很少仅仅局限于软件层面。

在嵌入式系统中,RAM不足往往意味着需要重新设计硬件、选用更大容量的微控制器,或在项目后期认证一个新的芯片型号。这一变化将波及整个组织:采购、认证、制造、长期供应规划,无一幸免。物料清单成本上升、项目进度延期、风险增加。

这便是RAM优化不只是技术问题,更是战略考量的原因所在。

为什么RAM优化比以往任何时候都更重要

与Flash不同,RAM在中低端微控制器中并不具备良好的扩展性。稍微增加RAM需求,往往迫使开发团队:

1、升级至更高系列的MCU家族

2、采用不同封装或引脚布局

3、增加额外功耗

4、开展新的认证与验证工作

对于长生命周期的产品——如传感器终端、系统控制器和工业网关——这些变更的代价极其高昂。如今,这一挑战变得更加严峻,因为全球市场力量对RAM的定价与供应影响日益加深,而这一力量往往来自嵌入式行业之外。

AI系统与超大规模数据中心需求的激增,彻底重塑了内存市场格局。训练和部署AI模型需要海量的高带宽内存,促使制造商优先生产利润率更高的产品并重新调配产能。

对于长生命周期的产品——如传感器终端、系统控制器和工业网关——这些变更的代价极其高昂。

如今,这一挑战变得更加严峻,因为全球市场力量对RAM的定价与供应影响日益加深,而这一力量往往来自嵌入式行业之外。

AI系统与超大规模数据中心需求的激增,彻底重塑了内存市场格局。训练和部署AI模型需要海量的高带宽内存,促使制造商优先生产利润率更高的产品并重新调配产能。

其结果是:

1、大宗内存芯片的生产吸引力下降

2、全市场供应配额收紧

3、定价压力波及整个内存生态系统

需要区分的是,这对不同嵌入式架构的影响并不相同。基于MCU的设计通常依赖片内RAM,其容量在芯片设计阶段就已固定,受外部内存市场影响较小。基于MPU的系统则相反,它们依赖片外DDR或LPDDR,其产能分配与其他大宗内存产品处于直接竞争状态。

尽管嵌入式系统并非AI级内存的目标市场,却同样无法置身事外。对于大批量产品而言,即使片外内存成本小幅上涨或供货略有波动,都会显著影响BOM成本、采购策略乃至产品的长期生存能力。而MCU虽受影响较为间接,但内存生态系统的持续压力,仍会在长期内影响定价、供货周期与架构决策。

主动管理RAM使用的团队,获得的远不止是释放出的字节,更是设计上的灵活度。他们可以在不触碰硬件的前提下,容纳功能扩展、安全更新及合规要求。

沉默的RAM消耗者:全局变量与静态变量

在实际项目中,最常见的现象之一便是全局变量与静态变量的缓慢累积。它们的引入本意良好:共享状态、方便使用、快速访问。久而久之,它们便成为RAM中的永久住户。

由于全局和静态对象贯穿系统整个生命周期,它们会:

1、从启动之初就占用可用内存

2、增加初始化开销

3、掩盖真实的运行时内存需求

在实践中,将变量从全局作用域移至函数内部,通常不会带来性能损失,而一旦函数退出,这部分RAM便立即释放。

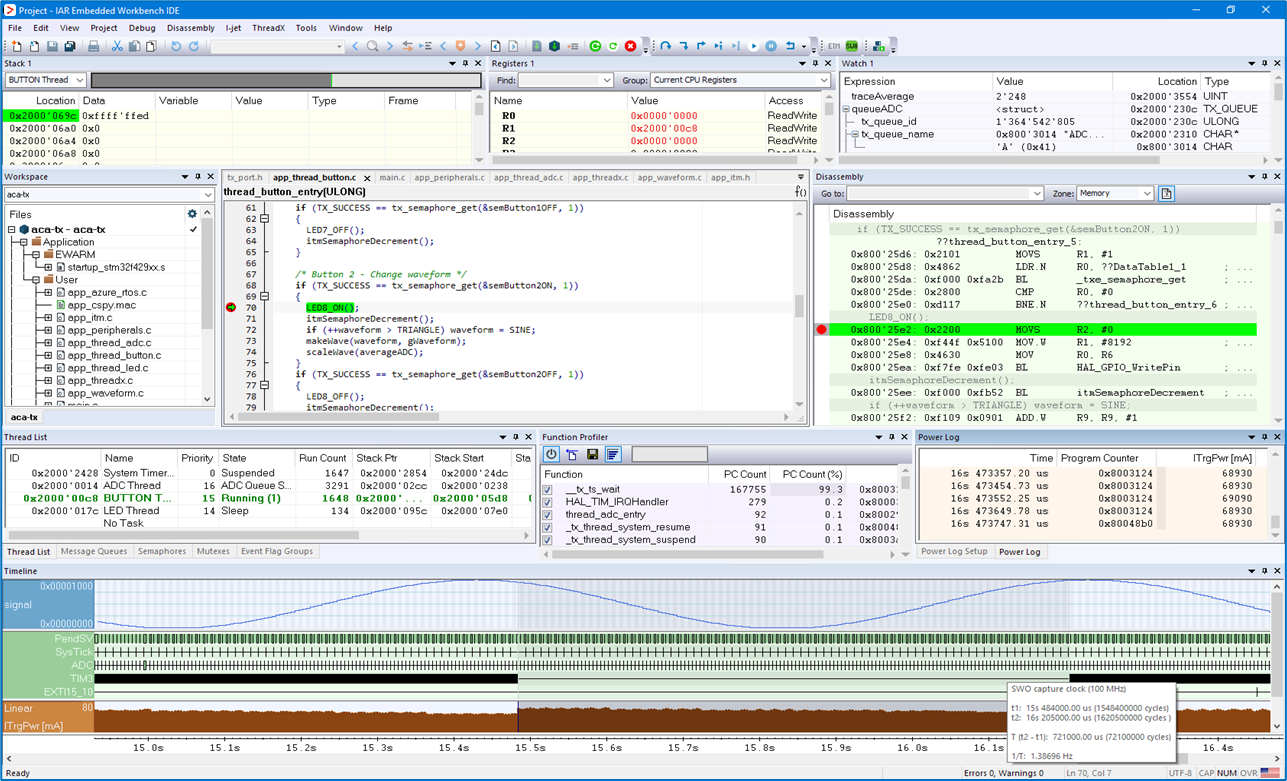

借助IAR链接器映射文件,这些长生命周期的内存分配情况一目了然。工程师无需猜测RAM的去向,可以直接查看具体是哪些模块和符号消耗了内存,并判断该内存是否真的需要常驻。

数据类型:小选择,大影响

在许多嵌入式系统中,内存浪费并非源于单一的重大失误,而是由成千上万个微小的选择累积而成。

在原本使用uint8_t就足够的情况下,却选择int,这便是典型的例子。单看一处,差异微乎其微。但遍布在数组、结构体、队列和堆栈中时,积少成多,影响巨大。

uint8_t status;

uint16_t measurement;

选择尺寸恰到好处的最小数据类型:

1、缩减RAM占用空间

2、提升缓存行为

3、通常还能改善性能与功耗

对于传感器密集的系统而言,这一点尤为重要,因为数据结构会被大量实例化,低效的设计会随产品复杂度的提升而成倍放大。

结构体布局与位域:隐藏的填充开销

即便是编写良好的代码,也可能因结构体填充与对齐而浪费RAM。

调整结构体成员的排列顺序,使用位域存储标志位,可以显著减少内存占用,尤其是当结构体被多次实例化或以数组形式存在时。

typedef struct

{

uint16_t value;

uint8_t state;

uint8_t flags : 3;

} DeviceStatus;

这些优化在运行时完全透明,但在链接器映射文件中却清晰可见,并最终反映在BOM成本上。

将常量数据留在它该在的地方:Flash

一个极其常见却常被忽视的RAM浪费源头,是在启动时被复制到RAM中的常量数据。字符串、查找表、配置数据,若不谨慎处理,便会悄无声息地吞噬宝贵的内存。

通过规范地使用const关键字,开发人员可以确保数据驻留在Flash中——这才是它们的归宿:

const uint16_t calibrationTable[128] = { /* Flash-resident */ };

借助IAR工具链,数据的存放位置是明确且可预测的。在受法规监管或安全至上的环境中,内存行为必须被清晰理解并有据可查,这一优势显得尤为重要。

动态分配:灵活,但危险

动态内存分配因其灵活性而颇具吸引力。然而在嵌入式系统中,这份灵活往往伴随着高昂的代价:

1、随时间推移产生内存碎片

2、不确定性的分配失败

3、难以调试的运行时崩溃

对于需要持续运行数月乃至数年的系统,采用动态分配的风险远大于收益。

许多团队采用以下方式取代堆内存使用:

1、静态缓冲区

2、固定大小的内存池

3、面向特定应用的分配器

最终收获的是可预测的内存行为、更简洁的测试流程,以及更高的系统可靠性——尤其在RAM余量紧张时,这一点至关重要。

堆栈使用:无形的故障模式

堆栈溢出是诊断难度最高的缺陷之一。它们可能仅在罕见条件下出现,或因调度与时序效应引发的特定任务交错而触发。

巨大的局部变量、过深的函数调用链,或递归调用,都可能迅速耗尽堆栈空间——在基于RTOS的系统中尤甚。

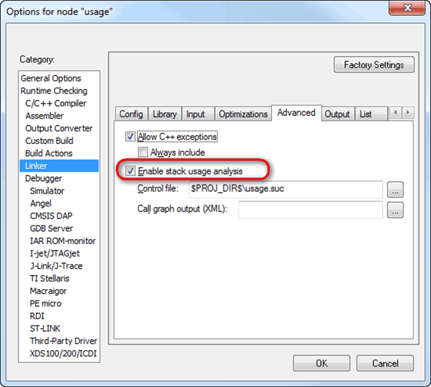

借助IAR的堆栈分析工具,开发人员能够:

1、估算最坏情况下的堆栈使用量

2、合理配置堆栈大小

3、规避那些难以复现的项目后期故障

编译器与链接器优化:不止于缩减代码尺寸

旨在优化代码尺寸(-Os)的编译器设定,通常与节省Flash存储空间挂钩,但它同样直接影响RAM占用:

1、减少临时变量数量

2、降低堆栈压力

3、缩减已初始化数据量

结合段垃圾回收机制与定期的链接器映射文件分析,这些技术能够有效防止内存占用在软件演进过程中悄无声息地持续攀升。

RTOS配置:按需取用,不为冗余付费

RTOS内核功能强大,但默认配置往往偏于保守。过大的堆栈分配、未被使用的功能特性、通用的参数设置,都会显著消耗RAM资源。

逐任务地调整RTOS配置文件,往往能够释放出足以避免一次硬件升级的内存空间。

从RAM优化到BOM成本节约

RAM优化的真正价值并非以字节衡量,而是体现在选项的多寡上。主动管理RAM使用的团队能够:

1、在较小容量的MCU型号上停留更长时间

2、规避项目后期的硬件变更

3、降低供应链风险

4、在不牺牲功能的前提下压缩BOM成本

借助 IAR 嵌入式开发平台,RAM的使用变得可见、可预测、可管理,内存优化也从一场被动救火,转变为一项可复现的工程实践。

总结

在嵌入式系统中,每一字节RAM都有其成本。有时,这份成本体现在硅片上。有时,它显露于项目进度、认证流程或供应链环节。

当全球内存需求日益被AI与数据中心所主导,即便是“纯粹”的嵌入式系统也同样感受到压力。

通过将RAM视为头等设计约束,并借助合适的工具加以管控,嵌入式团队能够打造出不仅高效,且具备经济韧性的系统。

下一步?

探索IAR如何优化您的嵌入式开发项目。尝试互动Demo,了解IAR平台,探索我们解决方案的先进功能。