Up-coming

Microelectronics US 2026

- 22-23 Apr, 2026

Join us at Microelectronics US to explore how engineering teams are building secure, reliable, and scalable embedded systems for real-world applications across industries such as automotive, industrial automation, and IoT.

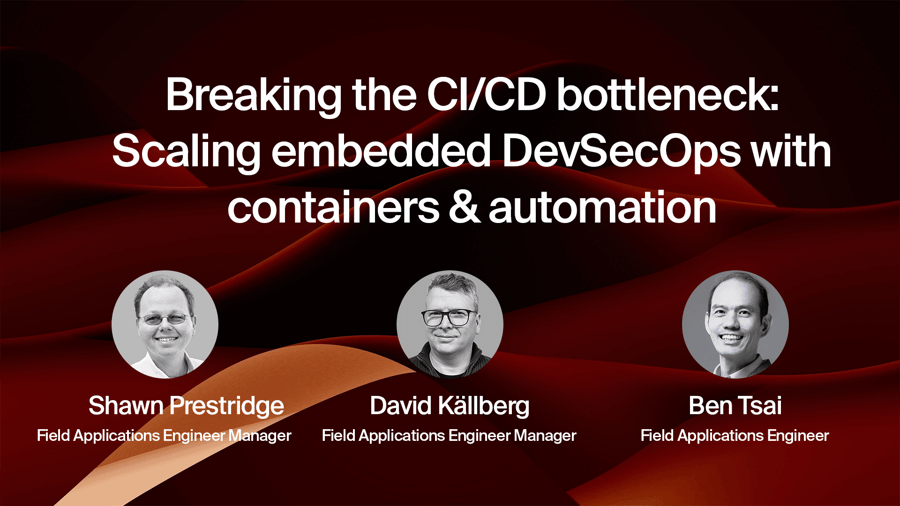

.png?width=900&height=506&name=EMEAAPAC%20-%20Breaking%20the%20smart%20industry%20bottleneck%201920%20x%201080%20(Presentation).png)

.png?width=900&height=506&name=AMERICAS%20-%20Breaking%20the%20smart%20industry%20bottleneck%20-%201920%20x%201080%20(Presentation).png)

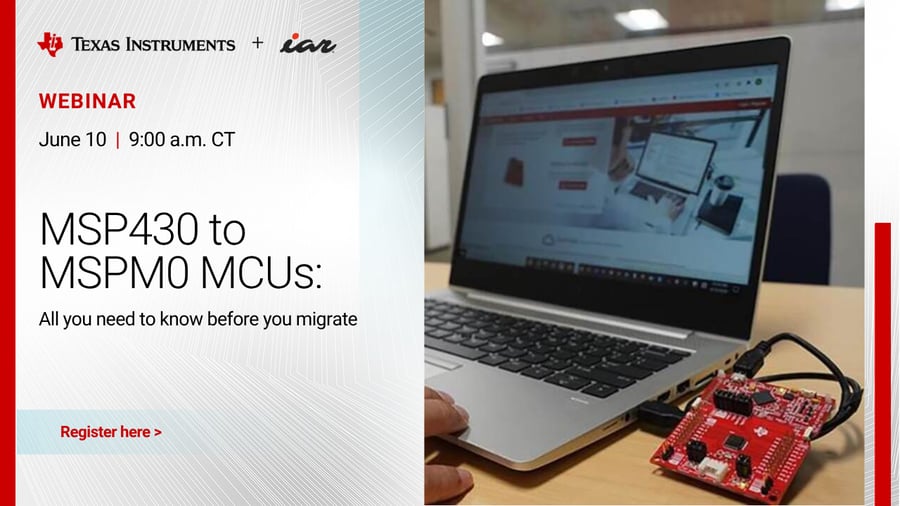

.jpg?width=900&height=506&name=Namnl%C3%B6s%20design%20(1).jpg)